# **PCIO**

# Peripheral Component Interconnect Input Output Controller

THE NETWORK IS THE COMPUTER

#### **Sun Microelectronics**

A Sun Microsystems, Inc. Business 2550 Garcia Avenue Mountain View, CA 94043 USA 415 960-1300 fax 415 969-9131

Part No.: 802-7837-01 March 1997

Copyright © 1997 Sun Microsystems, Inc. 2550 Garcia Avenue, Mountain View, California 94043-1100 U.S.A. All rights reserved. The information contained in this document is provided "As is" without any express representations of warranties. In addition, sun microsystems, inc. disclaims all implied representations and warranties, including any warranty of merchantability, fitness for a particular purpose, or non-infringement of third party intellectural property rights.

This document contains proprietary information of Sun Microsystems, Inc. or under license from third parties. No part of this document may be reproduced in any form or by any means or transferred to any third party without the prior written consent of Sun Microsystems, Inc.

Sun, Sun Microsystems and the Sun Logo are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States and other countries. All SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The information contained in this document is not designed or intended for use in on-line control of aircraft, aircraft navigation or aircraft communications; or in the design, construction, operation or maintenance of any nuclear facility. Sun disclaims any express or implied warranty of fitness for such uses.

# **Contents**

### 1. Introduction 1

Objectives 1

Key Device Features 1

**Intended Applications 2**

#### Functional Overview 3

Major Component Blocks 3

Bus Adapter 4

Channel Engine Interface 5

EBus2 Channel Engine 5

Ethernet Channel Engine 5

Scan Control Block 5

## Programmer's Model 7

Address Map 7

PCI Bus Configuration Space 7

Command Register 10

Status Register 10

Expansion ROM 11

Diagnostics Register 12

EBus2 Channel Engine 13

Ethernet Channel Engine 13

## 4. Bus Adapter 15

Introduction 15

Address Map 15

Bus Adapter Blocks 16

Block Diagram 16

Input Datapath 16

Output Datapath 17

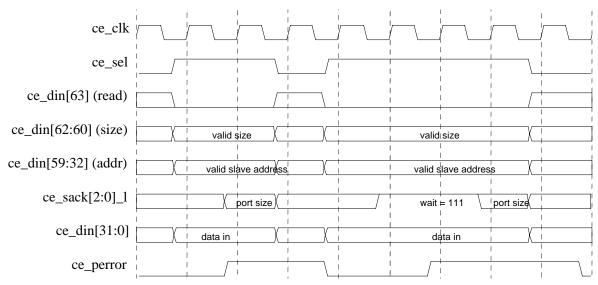

Configuration Space 18

**Interrupt Router 21**

Control Logic 22

PCI Bus Control 22

CEI Control 22

PCI Compatibility 23

Little Endian-ness 23

Commands 23

**Basic Transfer Control 24**

Addressing 24

Byte Alignment 25

**Transaction Termination 25**

Fast Back-to-Back 26

```

Exclusive Access 27

Device Selection 27

5. Channel Engine Interface 29

Goals 29

Terminology/Glossary 29

Signals 30

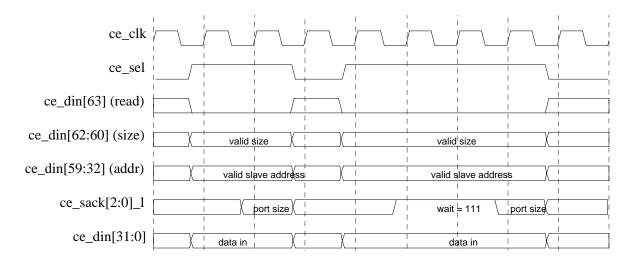

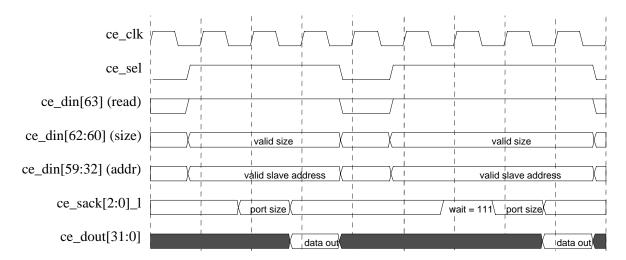

Transactions 33

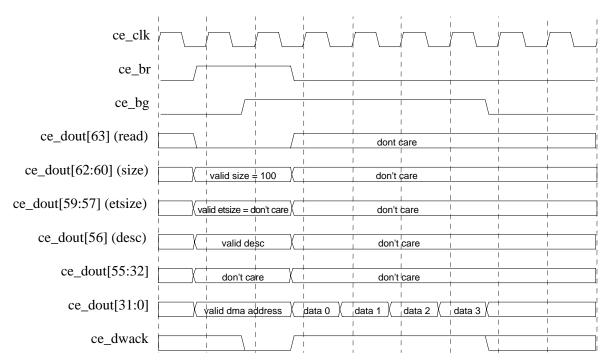

Slave Write 33

Slave Read 34

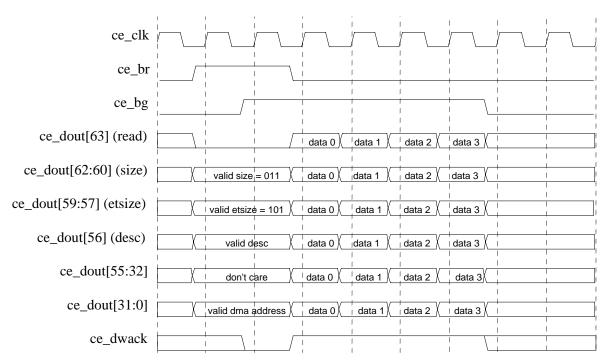

DMA Write (Channel Engine to Memory) 35

Data Ports 37

Error Handling & Reporting 38

Slave Transactions 38

Parity 38

Late Error 39

Access Error and Bus Sizing 40

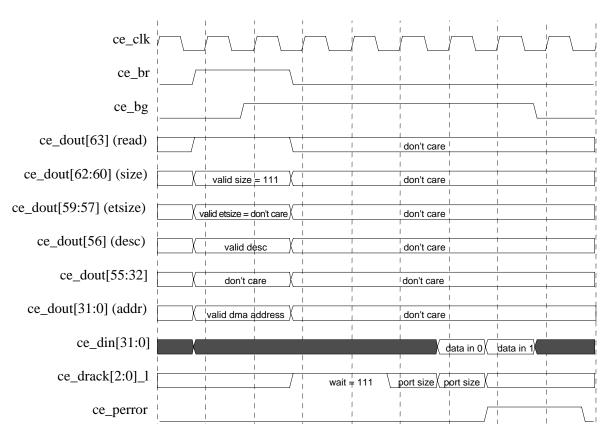

DMA Transactions 40

Parity 40

Late Error 40

Bus Errors 41

Bus Sizing 41

Arbitration 41

Design Guidelines 41

Timing 41

```

**Arbitration Parking 26**

Latency 26

# Cycle Time Budget Allocation 41 Signal Loading 42

### 6. Ethernet Channel Engine 43

Introduction 43

Overview 43

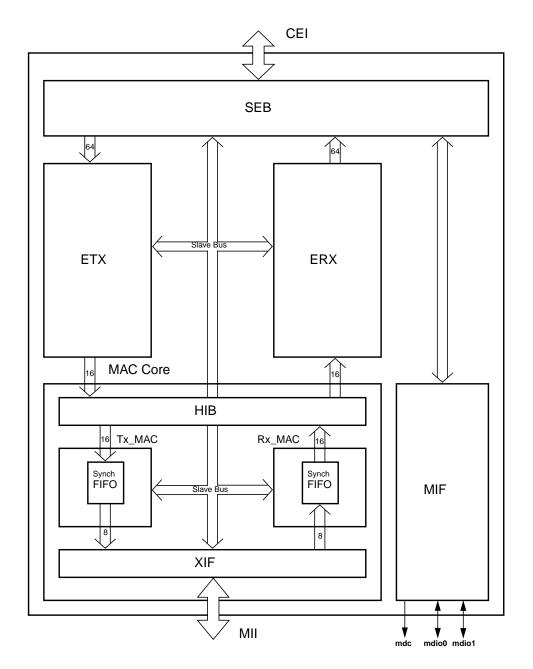

Major Components 45

**Functional Blocks** 45

Interfaces 45

Features List 46

Functional Description 46

Overview 47

Hardware Architecture 47

Functional Blocks 48

Interfaces and Data Paths 57

**Clock Domains** 59

Host Memory Data Management 61

Transmit Data Descriptor Ring 61

Receive Free Buffer Descriptor Ring 61

Local Memory Data Management 62

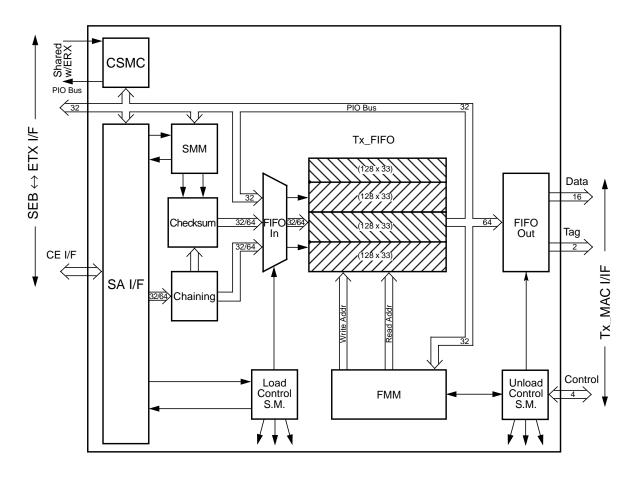

Transmit FIFO Data Structures 62

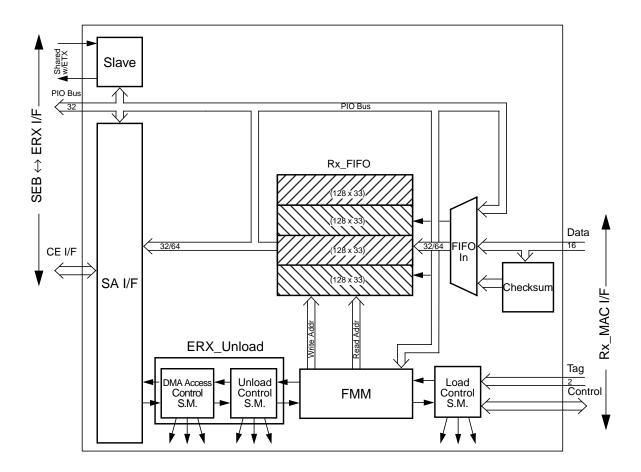

Receive FIFO Data Structures 63

Theory of Operation and Data Flow 63

**Transmit Operation 63**

- ▼ TxFIFO Load Process 63

- ▼ TxFIFO Unload Process 65

Receive Operation 65

- **▼** RxFIFO Load Process 65

- ▼ RxFIFO Unload Process 66

Error Conditions and Recovery 67

Fatal Errors 67

Non-fatal Errors 68

Programmer's Reference Guide 70

Overview 70

Host Memory Data Structures 70

Transmit Data Structures 71

Receive Data Structures 72

Local Memory Data Structures 74

TxFIFO Data Structures 76

RxFIFO Data Structures 76

Other User Accessible Resources 76

SEB Programmable Resources 79

ETX Programmable Resources 83

ERX Programmable Resources 87

MAC Programmable Resources 90

MIF Programmable Resources 101

**Programming Notes** 105

**Initialization Sequences** 105

**▼** Global Initialization 105

Memory Map 107

### 7. EBus2 Channel Engine 111

Introduction 111

Features 111

```

Address Map 113

```

EBus2 Slave Interface Description 116

Functional Description 116

Address Phase 116

Data Phase 116

Byte Stacking 117

**Buffered Slave Transfers** 117

IOCHRDY 117

Slave Transfer Size 117

#### EBus2 DMA Interface Description 117

**Functional Description 118**

Transfers From System Memory (DMA Read) 118

Transfers To System Memory (DMA Write) 118

Chained Mode 119

End of Transfer (Terminal Count) 119

EBus2 Device Acknowledgment 119

Host Bus Errors 120

Differences between EBus2 DMA Engine and SCSI DMA of DMA2 120

Priority Mechanism 121

Level 1 121

Level 2 121

Data Rates of EBus2 DMA Devices 122

DMA Testing 122

EBus2 Register Description 123

**AUXIO Registers** 123

Floppy AUXIO Register 123

Audio AUXIO Register 124

Power AUXIO Register 124

LED AUXIO Register 124

PCI/Mode AUXIO Register 125

Frequency AUXIO Register 125

SCSI Oscillator AUXIO Register 126

Temperature Sense AUXIO Register 126

Timing Control Registers 127

Timing Control Register 1 (TCR1) 127

Timing Control Register 2 (TCR 2) 129

Timing Control Register 3 (TCR3) 132

DMA Registers 133

DMA Control and Status Register (DCSR) 134

DMA Address Count Register (DACR) and DMA Next Address Register (DNAR) 138

DMA Byte Count Register (DBCR) and DMA Next Byte Register (DNBR) 139

Programming Notes 140

Timing Control Register Programming 140

Slave Cycle Time Programming 140

DMA Priority Programming 141

DMA Cycle Time Programming 141

DMA Register Programming 142

To set up a transfer to or from the EBus2 device using the DMA engine 142

To stop a transfer to or from the EBus2 device using the DMA engine 142

Use of Internal Byte Counter with Next Address feature disabled 142

Use of Internal Byte Counter with Next Address feature enabled 143

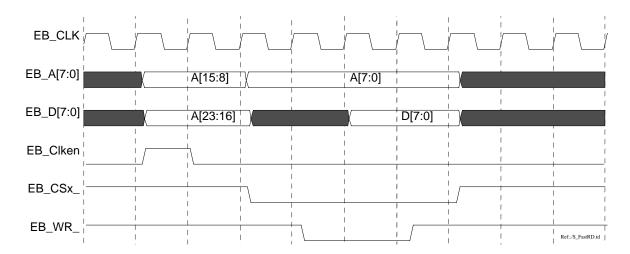

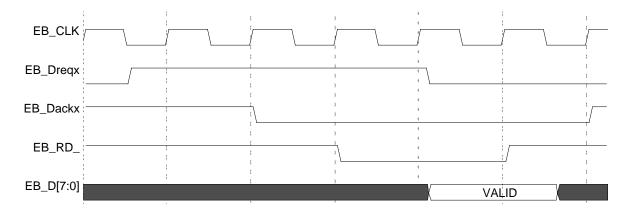

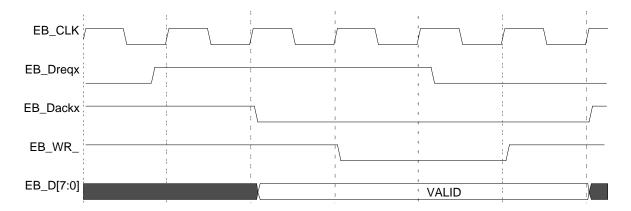

Timing Diagrams 147

EBus2 Slave Cycles 147

Ebus2 DMA Cycles 148

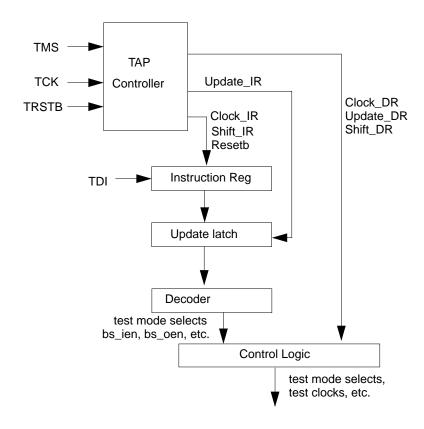

#### 8. Clock and Scan Control 149

Introduction 149

Test and Debug Modes 149

Boundary Scan Modes 149

ATPG Mode 150

Debug modes 150

Dumping internal state 150

Clock Controller 150

JTAG Controller 151

Control logic 152

Scan Data Paths 153

JTAG Instructions and ID 154

# Figures

| PCIO Block Diagram 4                                             |

|------------------------------------------------------------------|

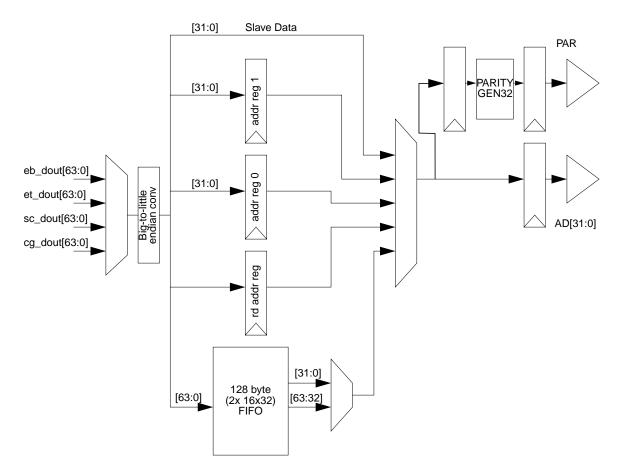

| Bus Adapter Block Diagram 17                                     |

| Bus Adapter Input Datapath 18                                    |

| Bus Adapter Output Datapath 19                                   |

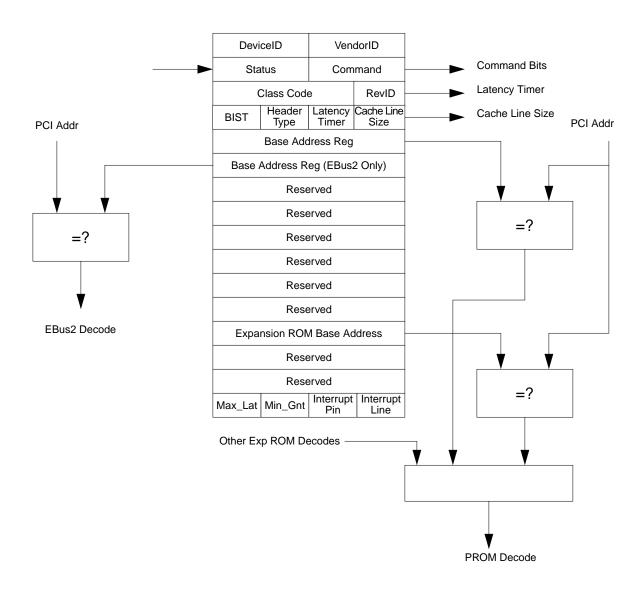

| Configuration Space and Address Decoders 20                      |

| Slave Write Transactions 34                                      |

| Slave Read Transactions 35                                       |

| DMA (Master) Write Transaction: 32-bit - 16-byte burst 36        |

| DMA (Master) Write Transaction: Extended Mode - 32-byte burst 37 |

| DMA (Master) Read Transaction: 32-bit - 8-byte burst 38          |

| Reporting a parity error during a slave write 39                 |

| FEPS Block Diagram 44                                            |

| Ethernet Channel Engine 49                                       |

| Transmit DMA Channel 54                                          |

| Receive DMA Channel 57                                           |

| Ethernet Channel Clock Domains 60                                |

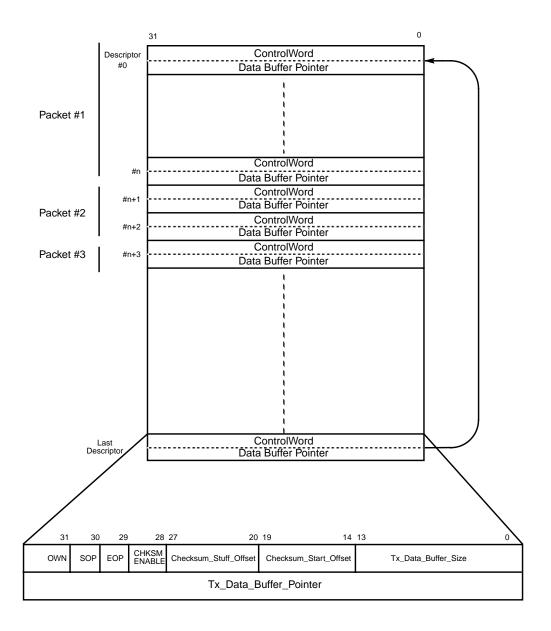

Transmit Host Data Structure 73

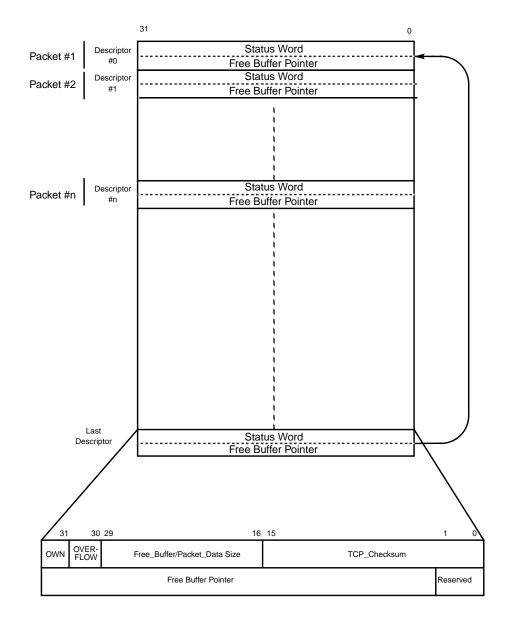

Receive Host Data Structure 75

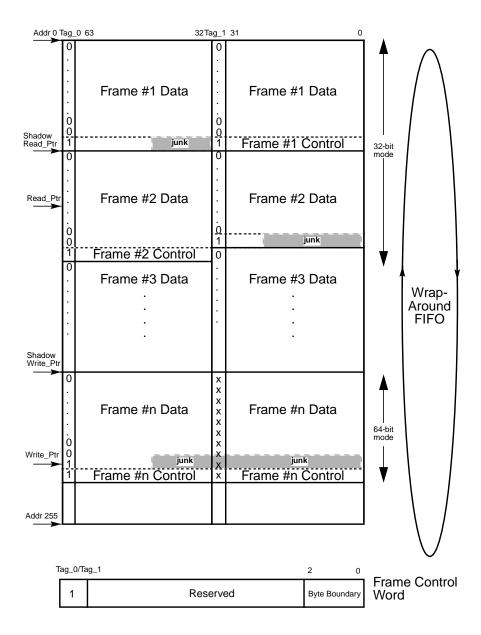

TxFIFO Organization 77

RxFIFO Organization 78

EBus2 channel engine block diagram 112

Programmable timing parameters 127

EBus2 slave read cycle 147

EBus2 Slave write cycle 147

EBus2 DMA read cycle 148

EBus2 DMA write cycle 148

JTAG Logic Block Diagram 152

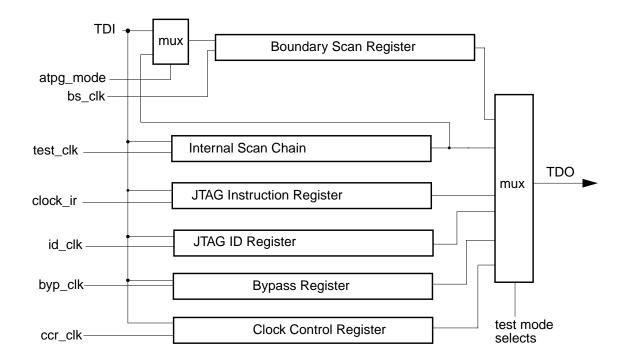

PCIO Scan Registers 153

# **Tables**

| PCIO PCI Configuration Space 7                                       |

|----------------------------------------------------------------------|

| Command Register Bits 10                                             |

| Status Register Bits 11                                              |

| Diagnostics Register Bits 12                                         |

| "Intelligent" Little-to-Big Endian Conversion 21                     |

| PCI Bus Commands Implemented and Generated by PCIO 24                |

| Channel Engine Interface Signals 30                                  |

| Slave Access Encoding of ce_din and ce_dout 32                       |

| DMA Transaction Encoding of ce_din and ce_dout 32                    |

| Transmit Data Structures: Descriptor Layout - Control Word 71        |

| Transmit Data Structures: Descriptor Layout - Data Buffer Pointer 71 |

| Receive Data Structures: Descriptor Layout – Status Word 72          |

| Receive Data Structures: Descriptor Layout – Free Buffer Pointers 74 |

| TxFIFO Data Structures: Control Word Layout 76                       |

| RxFIFO Data Structures: Status Word Layout 76                        |

| Software ResetRegister 79                                            |

|                                                                      |

Global Configuration Register 80

Global Status Register 81

ETX Configuration Register 84

ETX State Machine Register 86

ERX Configuration Register 87

ERX State Machine Register 89

XIF Configuration Register 90

TX\_MAC Configuration Register 92

TX\_MAC State Machine Register 96

RX\_MAC Configuration Register 97

RX\_MAC State Machine Register 100

MIF Configuration Register 102

MIF Frame/Output Register 103

MIF Status Register 104

MIF State Machine Register 105

Ethernet Channel Engine Address Map 107

EBus2 Address Map 113

DMA registers 115

Encoding of Timing control register 3 PR bit 121

Data rate and Latency tolerance of EBus2 DMA devices 122

Floppy AUXIO register bit definitions 124

Audio AUXIO register bit definitions 124

Power AUXIO register bit definitions 124

LED AUXIO register bit definitions 125

PCI/Mode AUXIO register bit definitions 125

Frequency AUXIO register bit definitions 126

SCSI oscillator AUXIO register bit definitions 126

Temperature sense AUXIO register bit definitions 126

Recovery Time (Trec) based on TCR1 bit encoding 128

Strobe width (Tstrb) based on TCR1 bit encoding 128

Tsu and Thld based on TCR1 bit encoding 128

Timing control register 1 (TCR1) bit definitions 129

Recovery Time (Trec) based on TCR2 bit encoding 130

Strobe width (Tstrb) based on TCR2 bit encoding 130

Setup time (Tsu) and hold time (Thld) based on TCR2 bit encoding 131

Timing control register 2 (TCR2) bit definitions 131

Encoding of timing parameters 132

Timing control register 3 (TCR3) bit definitions 132

EBus2 DMA CSR Register 134

Encoding for the BURST\_SIZE bits 137

DACR and DNAR bits 138

DBCR and DNBR bits 139

Scan Chain Lengths 153

JTAG ID fields 154

JTAG Instructions 154

# Introduction

The PCIO is a high integration, high performance single chip IO subsystem, interfacing to the PCI Local Bus. Off a single PCI bus load, it integrates high speed Ethernet and EBus2, a generic, slave-DMA bus to which are connected off-the-shelf peripherals implementing the rest of the Sun core IO system.

# 1.1 Objectives

The objectives for PCIO are a reflection of the systems it is targeted to. These are primarily cost-sensitive, high performance, single and multi processor desktops. The objectives include:

- Low cost

- Time-to-volume/time-to-market

- Complete IO subsystem: Ethernet, keyboard, mouse, serial ports, parallel port, stereo audio, floppy disk, boot PROM and time-of-day/non-volatile RAM

- High performance: high bandwidth, low interrupt overhead, tolerant of relatively high interrupt and bus latencies

- Modularity, at the architectural, design and test levels

- Full compliance with Sun and industry standards

- Suitability for licensing and third party marketing

# 1.2 Key Device Features

The following functions are built-in:

- PCI Local Bus master/slave interface, compliant with *PCI Local Bus Specification*, *Revision 2.0*<sup>1</sup>

- 10baseT (802.3) and 100baseT (802.30) Ethernet, using derivative of MAC, with fully buffered transmit and receive channels; media-independent interface (MII)

- Expansion bus interface (EBus2), supporting eight external devices and four buffered slave-DMA channels

- Oscillator for 40 MHz SCSI clock, and free running 10 MHz real-time clock

- IEEE 1149.1 JTAG compliant test architecture

The following functions are implemented with off-the-shelf devices, interfacing directly to the EBus2 interface:

- National Semiconductors<sup>™</sup> PC87303VLJ Super IO, integrating 82077-compatible floppy controller with DMA, parallel port, P1284-compliant, with ECP and EPP with DMA and two 16C550 serial controllers with 16-byte FIFOs, for keyboard and mouse

- Two high performance sync/async serial ports, using Siemens' SAB82532. 460.8 KBaud async, 384 Kbaud sync.

- Sun-compatible NVRAM, MK48T59, with alarm clock interrupt for power management

- EPROM or flash EPROM, 8-bit wide, up to 16 Mbyte, for boot or Fcode

- CS4231 Audio CODEC

- Access to USC and DSC EBus control port

- Auxiliary IO ports, for power supply control, temperature sensor, frequency calibration and other miscellaneous functions

# 1.3 Intended Applications

PCIO is being designed as part of the Ultra AX program. Ultra AX is a single processor, UltraSPARC based desktop using the PCI bus as its IO bus.

In addition, PCIO can be used on any system with a standard PCI bus. In 'motherboard' mode it makes the PROM available for boot code; in 'add-in' mode it can be used in card adapters or as a secondary motherboard design.

<sup>1.</sup> Although designed to the PCI 2.0 specification, PCIO is compatible with the 2.1 specification as well. However, certain 2.1-recommended features, such as pseudo-split reads and a tighter interpretation of the initial latency rule are not implemented

# **Functional Overview**

This chapter identifies and provides a brief description of each of the major component blocks in PCIO.

# 2.1 Major Component Blocks

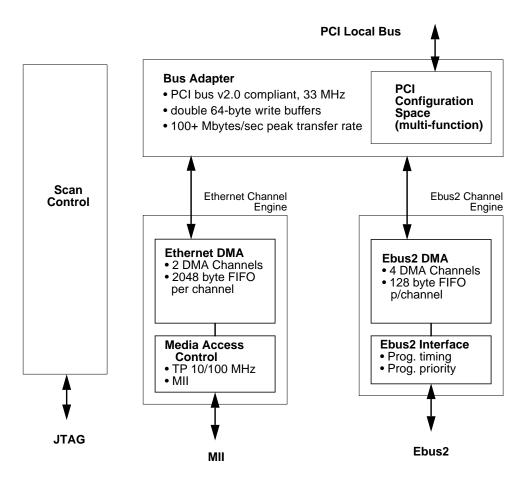

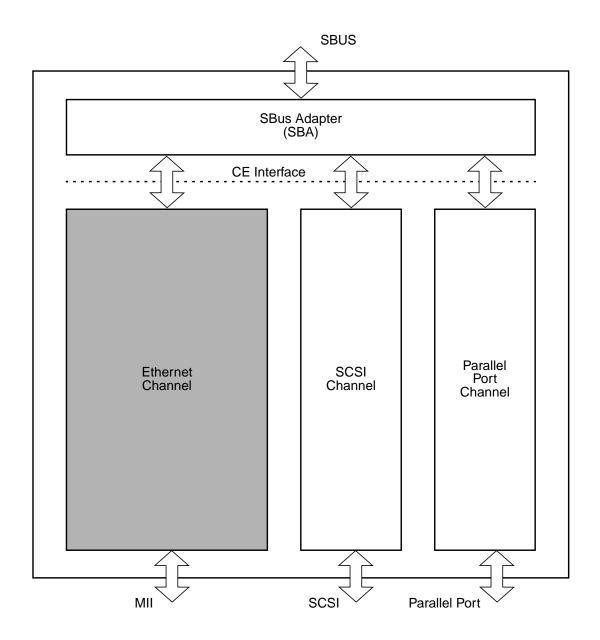

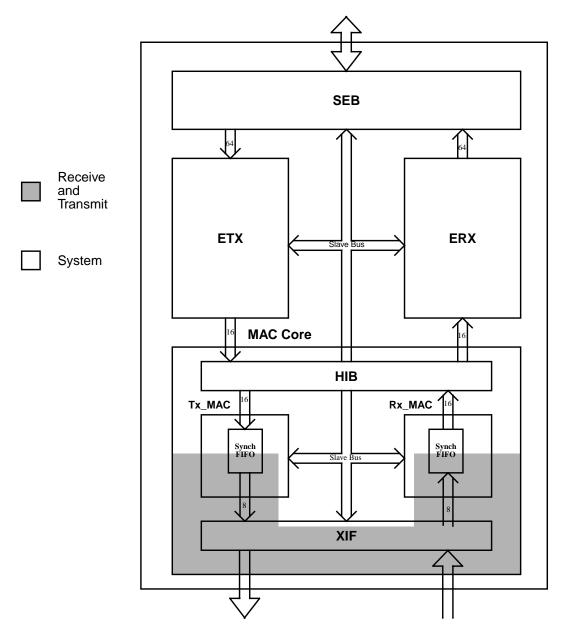

FIGURE 2-1 contains the block diagram for PCIO, showing the major component blocks. PCIO is built around an internal bus, the Channel Engine Interface, which provides the key to its modularity. Above the Channel Engine Interface, the Bus Adapter connects to the PCI bus. The two identical ports on the Channel Engine Interface are used for each of PCIO's functional units: Ethernet and Ebus2. Each of these has its own set of control and status registers, data buffers and the core logic function.

FIGURE 2-1 PCIO Block Diagram

# 2.1.1 Bus Adapter

The Bus Adapter provides a bus-independent layer between the channel engines and the PCI bus. The PCI bus interface is 32-bit and 33 MHz, fully compliant with the *PCI Local Bus Specification, Revision 2.0.* As a master, it is capable of 64-byte (8 word) bursts. DMA writes are buffered in the Bus Adapter to support back to back transactions.

The Bus Adapter also contains the PCI bus Configuration Space. PCIO presents itself to PCI as a multi-function device: Ebus2 (a bridge) and Ethernet. Each function has its own area in the configuration space.

## 2.1.2 Channel Engine Interface

The Bus Adapter contains two identical Channel Engine Interface ports, one for each channel engine. The Channel Engine Interface is a bus independent interface, resulting in a high level of modularity at the design and test level.

## 2.1.3 EBus2 Channel Engine

The EBus2 Channel Engine interfaces standard off-the-shelf devices to PCIO. Up to eight single or multi-function Intel-style 8-bit devices can be accommodated with a minimum of glue logic. Four internal DMA engines can be attached to any of these devices, buffering data streams in 128-byte FIFOs for each channel.

The standard set of IO devices is: PC87303VLJ Super IO (integrates 82077 floppy controller, dual 16C550 serial controllers for keyboard and mouse and ECP/EPP P1284 parallel port), SAB82532 serial communications controller, CS4231 audio CODEC, MK48T59 NVRAM with alarm clock, boot PROM and USC/DSC control port.

The EBus2 Channel Engine provides access to several general purpose IO lines (*a.k.a.* AUXIO), used to control miscellaneous system functions.

## 2.1.4 Ethernet Channel Engine

The Ethernet Channel Engine provides a buffered full duplex DMA engine and a Media Access Control function based on MAC. The descriptor-based DMA engine contains independent transmit and receive channels, each with 2048 bytes of on-chip buffering. The MAC provides a 10 or 100 Mbps CSMA/CD protocol based network interface conforming to IEEE 802.3, proposed IEEE 802.30 and Ethernet specifications.

### 2.1.5 Scan Control Block

The Scan Control contains a tap controller.

# Programmer's Model

# 3.1 Address Map

## 3.1.1 PCI Bus Configuration Space

PCIO's PCI Configuration space complies with the PCI Bus Specification v2.0. Unless otherwise indicated, all the configuration space is accessible as bytes, halfword and word, and is read/write.

PCIO contains two functions within a single device: EBus2 and Ethernet. These are implemented as functions 0 and 1 respectively. PCIO responds to configuration cycles for functions 2 to 7 indicating they are not implemented (i.e. read zeroes from all locations.)

Detailed information on the PCI configuration space can be found in Chapter 6 of the PCI bus specification.

**Note** – All multi-byte configuration fields are in LITTLE ENDIAN format

Table 3-1 PCIO PCI Configuration Space

| Offset        | Size   | R/W | Name               |

|---------------|--------|-----|--------------------|

| EBus2         |        |     |                    |

| 0x000 - 0x001 | 16-bit | RO  | Vendor ID = 0x108E |

| 0x002 - 0x003 | 16-bit | RO  | Device ID = 0x1000 |

PCIO PCI Configuration Space (Continued) Table 3-1

| Offset        | Size   | R/W | Name                                                                                                                                                                                                                         |

|---------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x004 - 0x005 | 16-bit | RW  | Command Register                                                                                                                                                                                                             |

| 0x006 - 0x007 | 16-bit | RW  | Status Register                                                                                                                                                                                                              |

| 0x008         | 8-bit  | RO  | Revision ID = 0x01                                                                                                                                                                                                           |

| 0x009 - 0x00B | 24-bit | RO  | Class Code<br>0x00B Base Class = 0x06 Bridge Device<br>0x00A Sub Class = 0x80 Other Bridge<br>0x009 Prog i/f = 0x00                                                                                                          |

| 0x00C         | 8-bit  | R/W | Cache Line Size, in units of 32-bit words; resets to 0x00                                                                                                                                                                    |

| 0x00D         | 8-bit  | R/W | Latency Timer                                                                                                                                                                                                                |

| 0x00E         | 8-bit  | RO  | Header Type = 0x80, identifies multi-<br>function device, standard header type                                                                                                                                               |

| 0x00E         | 8-bit  | RO  | BIST = 0x00, not capable                                                                                                                                                                                                     |

| 0x010 - 0x013 | 32-bit | RW  | Base Address Register, Boot ROM, 16 Mbyte space: bits [23:0] read as zero; reset value depends on setting of boot[1:0] pins: 00 reset to 0x3000.0000 01 reset to 0x7000.0000 10 reset to 0xB000.0000 11 reset to 0xF000.0000 |

| 0x014 - 0x017 | 32-bit | RW  | Base Address Register, EBus2 Channel<br>Engine, 8 Mbyte space; bits [22:0] read as<br>zero; resets to 0xF100.0000                                                                                                            |

| 0x018 - 0x02F |        |     | Reserved, read as zero                                                                                                                                                                                                       |

| 0x030 - 0x033 | 32-bit | RW  | Expansion ROM Base Address, 16 Mbyte space: bits [23:0] read as zero; resets to 0x0000.0000                                                                                                                                  |

| 0x034 - 0x03B |        |     | Reserved, read as zero                                                                                                                                                                                                       |

| 0x03C         | 8-bit  | RW  | Interrupt Line                                                                                                                                                                                                               |

| 0x03D         | 8-bit  | RO  | Interrupt Pin = 0x01, use INTA# if ADD-IN mode = 0x00, if MOTHERBOARD mode                                                                                                                                                   |

| 0x03E         | 8-bit  | RO  | Min_Gnt = $0x0A$ , in units of $1/4$ of a microsecond = $2.5 \mu S$                                                                                                                                                          |

| 0x03F         | 8-bit  | RO  | Max_Lat = 0x19, in units of 1/4 of a microsecond = $6.25 \mu S$                                                                                                                                                              |

|               |        |     |                                                                                                                                                                                                                              |

PCIO PCI Configuration Space (Continued) Table 3-1

| Offset        | Size   | R/W | Name                                                                                                                  |

|---------------|--------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 0x044-0x0FF   |        |     | Reserved, read as zero                                                                                                |

| Ethernet      |        |     |                                                                                                                       |

| 0x100 - 0x101 | 16-bit | RO  | Vendor ID = 0x108E                                                                                                    |

| 0x102 - 0x103 | 16-bit | RO  | Device ID = 0x1001                                                                                                    |

| 0x104 - 0x105 | 16-bit | RW  | Command Register                                                                                                      |

| 0x106 - 0x107 | 16-bit | RW  | Status Register                                                                                                       |

| 0x108         | 8-bit  | RO  | Revision ID = 0x01                                                                                                    |

| 0x109 - 0x10B | 24-bit | RO  | Class Code<br>0x00B Base Class = 0x02 Network Device<br>0x00A Sub Class = 0x00 Ethernet<br>0x009 Prog i/f = 0x00      |

| 0x10C         | 8-bit  | R/W | Cache Line Size, in units of 32-bit words; resets to 0x00                                                             |

| 0x10D         | 8-bit  | R/W | Latency Timer                                                                                                         |

| 0x10E         | 8-bit  | RO  | Header Type = 0x80, identifies multi-<br>function device, standard header type                                        |

| 0x10E         | 8-bit  | RO  | BIST = 0x00, not capable                                                                                              |

| 0x110 - 0x113 | 32-bit | RW  | Base Address Register, Ethernet Channel<br>Engine, 32 Kbyte space; bits [14:0] read as<br>zero; resets to 0x0000.0000 |

| 0x114 - 0x117 |        |     | Reserved, read as zero                                                                                                |

| 0x118 - 0x12F |        |     | Reserved, read as zero                                                                                                |

| 0x130 - 0x133 | 32-bit | RW  | Expansion ROM Base Address, 16 Mbyte space: bits [23:0] read as zero; resets to 0x0000.0000                           |

| 0x134 - 0x13B |        |     | Reserved, read as zero                                                                                                |

| 0x13C         | 8-bit  | RW  | Interrupt Line                                                                                                        |

| 0x13D         | 8-bit  | RO  | Interrupt Pin<br>= 0x02, use INTB# if ADD-IN mode<br>= 0x00, if MOTHERBOARD mode                                      |

| 0x13E         | 8-bit  | RO  | Min_Gnt = $0x0A$ , in units of $1/4$ of a microsecond = $2.5 \mu S$                                                   |

| 0x13F         | 8-bit  | RO  | Max_Lat = 0x05, in units of 1/4 of a microsecond = 1.25 $\mu S$                                                       |

## 3.1.1.1 Command Register

The command register provides coarse control over a function's ability to generate and respond to PCI cycles. When a 0 is written to this register, the function is logically disconnected from the PCI bus for all accesses except configuration accesses. Each function in PCIO has its own command register.

**Note** – Please refer to §6.2.2 of the PCI bus specification for more information on the command register

Table 3-2 Command Register Bits

| Bit     | Usage                                                                                                                                                                                                                                          |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0       | IO Space — Not implemented, read back as zero                                                                                                                                                                                                  |  |  |

| 1       | Memory Space — Controls a function's response to memory space accesses: when set, allows the function to respond to memory space accesses. Reset to zero for Ethernet and for EBus2 in ADD-IN mode; reset to one for EBus2 in MOTHERBOARD mode |  |  |

| 2       | Bus Master — Controls a function's ability to act as a master on the PCI bus: when set, allows the device to behave as a bus master. Reset to zero                                                                                             |  |  |

| 3       | Special Cycles — Not implemented, read back as zero                                                                                                                                                                                            |  |  |

| 4       | Memory Write and Invalidate Enable — Controls whether a master can generate the Memory Write and Invalidate command (when set.) Reset to zero.                                                                                                 |  |  |

| 5       | VGA Palette Snoop — Not implemented, read back as zero                                                                                                                                                                                         |  |  |

| 6       | Parity Error Response — This bit controls the function's response to parity errors.                                                                                                                                                            |  |  |

| 7       | Wait Cycle Control — Not implemented, read back as zero                                                                                                                                                                                        |  |  |

| 8       | SERR# Enable — This bit is an enable for the SERR# driver: when set, the SERR# pin driver is enabled                                                                                                                                           |  |  |

| 9       | Fast Back-to-Back Enable — Not implemented, read back as zero                                                                                                                                                                                  |  |  |

| 15 - 10 | Reserved, read back as zero                                                                                                                                                                                                                    |  |  |

### 3.1.1.2 Status Register

The status register is used to record information for PCI bus related events. Reads to this register behave normally; during writes, bits can only be reset, but not set. A bit is reset whenever the register is written, and the data in the corresponding bit location is a 1. Each function in PCIO has its own status register.

**Note** – Please refer to §6.2.3 of the PCI bus specification for more information on the status register

Table 3-3 Status Register Bits

| Bit    | Usage                                                                                                                                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 - 0  | Reserved, read back as zero                                                                                                                                                                                                                   |

| 7      | Fast Back-to-Back Capable — Read-only, set to 1, indicates PCIO is capable of accepting fast back-to-back transactions                                                                                                                        |

| 8      | Data Parity Detected — Set when three conditions are met: 1) PERR# was asserted or observed asserted, 2) function was the bus master for the transaction in which the error occurred, 3) Parity Error Response bit in command register is set |

| 10 - 9 | DEVSEL Timing — Read-only, set to 01 (medium)                                                                                                                                                                                                 |

| 11     | Signaled Target Abort — When set, indicates the function terminated a transaction with a target-abort; this bit is implemented only in the EBus2 configuration space, it is read back as zero in Ethernet and SCSI                            |

| 12     | Received Target Abort — When set, indicates the function had a transaction terminated by a target-abort                                                                                                                                       |

| 13     | Received Master Abort — When set, indicates the function had a transaction terminated by a master-abort                                                                                                                                       |

| 14     | Signaled System Error — Set when any of the functions asserts SERR#; this bit is implemented only in the EBus2 configuration space, it is read back as zero in Ethernet                                                                       |

| 15     | Detected Parity Error — Set when a function detects a parity error and the Parity Error Response in the command register is set                                                                                                               |

## 3.1.1.3 Expansion ROM

Although both function units have Expansion ROM Base Address registers, the two spaces map to the same physical ROM device, which is the same device used as boot ROM. Offset 0x00 from the either Expansion ROM space or Boot ROM space will read the first byte of the EPROM.

## 3.1.1.4 Diagnostics Register

The diagnostics register in the EBus2 configuration space provides a means to force a variety of error and exception conditions into the system. Although this register is read-write, most of the bits are self-clearing: they will reset themselves after generating the desired condition.

In order to write to the diagnostics register, the enable\_diag\_reg bit (bit 31) must be written first. Writes with this bit reset are ignored.

All bits in this register reset to zero.

Table 3-4 Diagnostics Register Bits

| Bit    | Name                   | Usage                                                                                                                                                                                     |

|--------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bad_addr_parity_master | Computes wrong parity during address phases, when PCIO is bus master; will cause SERR# to be asserted by other devices in the bus (note: PCIO will not assert SERR# under this condition) |

| 1      | bad_addr_parity_slave  | Computes wrong parity during address phases, when PCIO is not the bus master; will cause SERR# to be asserted by PCIO                                                                     |

| 2      | bad_data_parity_master | Computes wrong parity during data phases, when PCIO is doing DMA writes; will cause PERR# to be asserted by the agent receiving data                                                      |

| 3      | bad_data_parity_slave  | Computes wrong parity during data phases, when PCIO is data receiver (PIO write and DMA read); will cause PCIO to assert PERR#                                                            |

| 4      | Reserved               | [Write Buffer Enable] - not implemented                                                                                                                                                   |

| 5      |                        | Reserved, read back as zero                                                                                                                                                               |

| 6      | gen_disconnect         | Causes PCIO to disconnect during a slave transaction, without returning any data                                                                                                          |

| 7      | gen_target_abort       | Causes PCIO to generate a target-abort during a slave transaction                                                                                                                         |

| 8      | use_byte_holes         | Causes PCIO to use the 4-bit mask in bits [12:9] as<br>the byte enables in the next transaction when<br>PCIO is a master                                                                  |

| 12 - 9 | byte_holes[3:0]        | Byte enable mask; used with use_byte_holes bit to generate byte holes in DMA streams                                                                                                      |

Diagnostics Register Bits (Continued) Table 3-4

| Bit     | Name            | Usage                                                                                                                                                                                                                                                            |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | arb_write       | Arbitrate PIO Writes, when set will force PIO writes to arbitrate for the CEI before proceeding; normally, arbitration is not needed, but setting this bit is required for running the diagnostic loopback from one DMA engine to another in EBus; reset to zero |

| 14      | force_swap      | This bit, when set, will cause any descriptor transfer in the CEI to undergo byte swapping, rather than passing straight through. Reset to zero.                                                                                                                 |

| 30 - 15 |                 | Reserved, read back as zero                                                                                                                                                                                                                                      |

| 31      | enable_diag_reg | enable_diag_reg:                                                                                                                                                                                                                                                 |

#### 3.1.2 EBus2 Channel Engine

The address map for registers in the EBus2 channel engine can be found in Table 7-1.

#### **Ethernet Channel Engine** 3.1.3

Addresses on the Ethernet Channel Engine are offset from the Base Address Register 0 in the Ethernet section of the configuration space (Configuration Space address 0x110.) The address map can be found in Table 6-23.

# **Bus Adapter**

## 4.1 Introduction

The Bus Adapter provides the layer between the bus-independent Channel Engine Interface and the PCI Local Bus. Its main features are as follows:

- Single time domain operates at the PCI Bus frequency

- PCI Local Bus Revision 2.0 compatibility, 32-bit only

- Full master and slave capabilities

- 64-byte bursts as initiator

- Multi-function configuration space, with independent address decoders for each function

- Dual-buffered DMA WRITE path

- Two Channel Engine Interface ports, 32/64-bit wide

- Interrupt router for PCI Bus add-in card or motherboard modes

# 4.2 Address Map

There are no addressable registers in the Bus Adapter accessible during normal device operation. The PCI Bus Configuration Space is only available during PCI configuration cycles and contains registers which set up PCIO's basic operating functions. The address map for the Configuration Space is in the "Address Map" section of Chapter 3, "Programmer's Model."

# 4.3 Bus Adapter Blocks

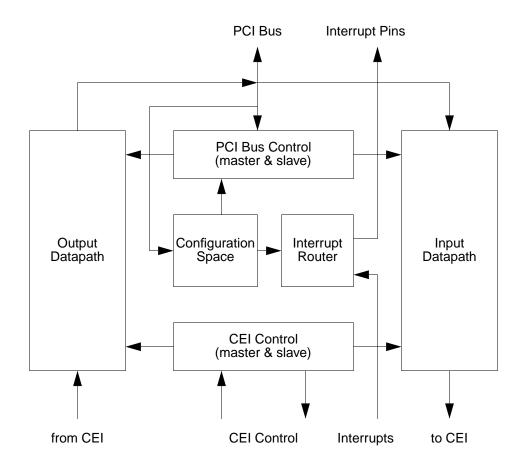

## 4.3.1 Block Diagram

FIGURE 4-1 contains the block diagram for the Bus Adapter. The Input Datapath contains pipeline registers and a 32-bit parity checker. The Output Datapath contains dual DMA write buffers, address registers for pending DMA transactions, and a 32-bit parity generator. The Configuration Space contains the registers defined by the PCI Bus Specifications, and address decoders. The Interrupt Router directs the different channel engine interrupts to independent interrupt pins or to PCI INTA, B, C and D. Finally, the Control Logic is composed of a PCI Bus Control, dealing with the PCI Bus and one end of both input and output datapaths, and the CEI Control, dealing with the Channel Engine Interface and the other end of the input and output datapaths.

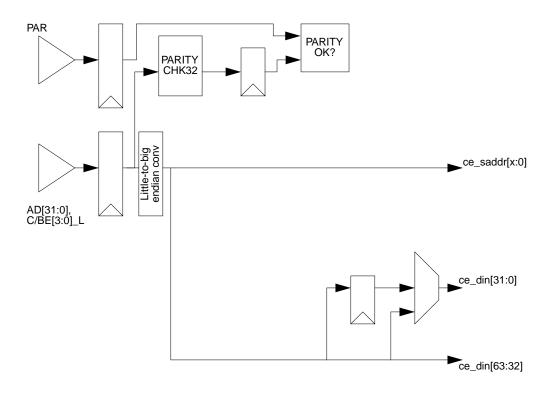

## 4.3.2 Input Datapath

A more detailed view of the Input Datapath is provided in FIGURE 4-2. The input datapath contains input pipeline registers on the PCI Bus signals, to minimize timing constraints. The pipelined data and command/byte enable bits are then checked for parity errors.

Address is sent to the Configuration Space where it is decoded. When any of the channel engines is decoded as the target for a write command, the pre-decoded address and data is stored in the write buffers, to accelerating PIO access. DMA read data received is sent to the CEI directly.

The input datapath also performs the conversion from the little endian PCI Bus to the big endian format of the channel engines. This conversion is "intelligent", based on the data object size (byte, half word, word or double word) and whether the data object is part of a DMA data stream or is PIO or descriptor data. A pseudo-code description of this conversion is shown in TABLE 4-1.

Finally, the input datapath interfaces to a 64-bit wide Channel Engine Interface, with DMA transactions on the CEI being either 32- or 64-bits wide. The input datapath can assemble successive 32-bit words on the PCI Bus into 64-bit words on the CEI.

FIGURE 4-1 Bus Adapter Block Diagram

## 4.3.3 Output Datapath

A more detailed view of the Output Datapath is provided in FIGURE 4-3. All PCI Bus outputs are registered, to minimize timing constraints. Parity for data and command/byte enables is generated and output with one PCI clock delay of its respective data.

Data coming from the CEI is converted from big endian to little endian format, as described in the input datapath and shown in TABLE 4-1. Addresses are not affected by the conversion.

FIGURE 4-2 Bus Adapter Input Datapath

Data coming in from the CEI is first multiplexed, depending on which channel engine has ownership of the CEI. DMA address pointers can be stored in any of two write address registers, or a single read address registers. Up to three DMA transactions can be pending or in process: a DMA read, and two DMA writes.

DMA data from the CEI comes in either 32- or 64-bit formats, and is assembled into a DMA write buffers. Up to two 64-byte DMA write bursts can be pending. The 64-bit data out of the buffer is multiplexed into the 32-bit PCI Bus width. A 32-bit wide slave data path is also provided for PIO read operations.

## 4.3.4 Configuration Space

The PCI Bus Configuration Space is used by power-on software (i.e. OpenBoot) to probe and initialize system resources. The configuration space is a collection of read-only and read-write memory locations, all of which can be read by the power-on

FIGURE 4-3 Bus Adapter Output Datapath

software using a configuration cycle. Some fields —Command, Latency Timer, Cache Line Size— are read-write fields with values visible to the PCI Bus Control logic at all times. The Status register has several inputs which are used to set and reset specific bits. Writing the Status register is by clearing bits only. More detailed information is available in the "PCI Bus Configuration Space" section of Chapter 3, "Programmer's Model." A diagram of the configuration space is shown in FIGURE 4-4.

The Address Decoders compare the address on the PCI Bus with the Base Address Registers (one or two) and Expansion ROM Base Address Register, when enabled by the "Memory Space" bit in the Command Register. The Expansion ROM Base Address Register has an additional Decode Enable bit within it.

FIGURE 4-4 Configuration Space and Address Decoders

If PCIO is in 'motherboard' mode, the EBus2 address decoders are enabled on power-on, for access to boot PROM. The Base Address Registers for the EBus2 resets to a value depending on the BOOT pins for PROM and 0xF100\_0000 for the other EBus2 devices. These address can be changed by the power-on software, to relocate either PROM or EBus2. Also, note that in 'motherboard' mode, the Memory Space bit in the Command Register for EBus2 has no effect.

TABLE 4-1 "Intelligent" Little-to-Big Endian Conversion

```

if PIO access then

case access size of

byte:{

pci_bits(31:24) goto channel_bits(7:0)

pci_bits(23:16) goto channel_bits(15:8)

pci_bits(15:8) goto channel_bits(23:16)

pci_bits(7:0) goto channel_bits(31:24)

half_word: {

pci_bits(31:16) goto bits(15:0)

pci_bits(15:0) goto bits(31:16)

word: pci_bits(31:0 goto channel_bits(31:0)

endcase

else if DMA access then

if data_stream then {

pci_bits(31:24) goto channel_bits(7:0)

pci_bits(23:16) goto channel_bits(15:8)

pci bits(15:8) goto channel bits(23:16)

pci_bits(7:0) goto channel_bits(31:24)

else if descriptor then

case access_size of

/* not necessary if PCIO does not use */

byte:{

pci bits(31:24) goto channel bits(7:0)

pci_bits(23:16) goto channel_bits(15:8)

pci_bits(15:8) goto channel_bits(23:16)

pci_bits(7:0) goto channel_bits(31:24)

half_word: {/* not necessary if PCIO does not use */

pci_bits(31:16) goto bits(15:0)

pci_bits(15:0) goto bits(31:16)

word: pci_bits(31:0 goto channel_bits(31:0)

endcase

```

# 4.3.5 Interrupt Router

The Interrupt Router directs the channel engines' interrupts to the appropriate device pins. In 'add-in' mode, PCI devices must use the INTA, B, C and D provided in the PCI Bus Specification. In PCIO, EBus2 interrupts (only those associated with a DMA channel) are assigned to INTA# and Ethernet interrupts are assigned to INTB#. In 'motherboard' mode, PCIO has separate interrupt lines for each internal device.

INTA# becomes enet\_irq\_l, INTB# is unused, INTC# becomes pport\_irq\_l and INTD# becomes fpy\_irq\_l; interrupts from audio capture are routed to audio\_cap\_irq\_l while interrupts from audio playback are routed to audio\_pb\_irq\_l.

In 'motherboard' mode, interrupts from external EBus2 devices not associated with DMA channels (*e.g.* keyboard and mouse) are connected directly to the system interrupt controller (RIC chip in Ultra AX). In 'add-in' mode, these interrupts need to be combined with INTA#, since all EBus2-related interrupts should be on a single interrupt pin.

# 4.3.6 Control Logic

There are two main blocks of control logic, the PCI Bus Control, with a slave and master portion, and the CEI Control.

## 4.3.6.1 PCI Bus Control

The slave portion of the PCI Bus Control monitors the PCI Bus for configuration or memory commands. Based on the address decoding in the configuration space, it will claim transactions for which PCIO is the target, asserting DEVSEL#. For PIO reads, it will direct the CEI Control to arbitrate for the CEI and perform a slave read transaction. When the CEI Control indicates data is ready, the PCI Bus Control will complete the PCI transactions.

The master portion of the PCI Bus Control initiates transactions on the PCI on behalf of any of the channel engines. For DMA writes, after the CEI Control has accepted data into the DMA write buffer, it will direct the PCI Bus Control to start a PCI transaction. After the transaction is completed, it will issue a transaction acknowledge back into the CEI for the channel engine to synchronize its data flow. For DMA reads, after the CEI Controls grants the CEI to a master requesting a read, it will direct the PCI Bus Control to initiate a PCI read transaction. As data is returned from the PCI target, it is passed along into the CEI and the waiting master.

### 4.3.6.2 CEI Control

The CEI Control performs arbitration on the CEI and controls loading of the DMA write buffers and data flows during DMA reads and slave reads and writes.

The CEI Control treats the CEI as two independent, unidirectional busses: an adapter-to-channel engine bus carrying slave address, slave write data and DMA read data, and a channel engine-to-adapter bus, carrying DMA address, slave read data and DMA write data. Different transactions can proceed at the same time as

long as they don't compete for resources. For example, a DMA write utilizes the channel engine-to-adapter bus exclusively, while a slave write utilizes the adapter-to-channel engine bus exclusively, and thus can proceed at the same time.

# 4.4 PCI Compatibility

PCIO conforms fully with the *PCI Bus Specification Revision 2.0.* PCIO is a 32-bit device, with 32-bit data and 32-bit address. All the PCI Bus I/O pads are "socket-compliant", having a dedicated power rail that can be either 3.3V or 5V. PCIO can be used in either 3.3V or 5V systems. The core logic in PCIO requires 5V.

PCIO is a multi-function device comprising network (Ethernet) and a bridge function (EBus2). There are no provisions for cache coherency built into PCIO.

## 4.4.1 Little Endian-ness

Like most other PCI Bus devices, PCIO conforms to the little endian byte ordering, that is, the most significant byte of a 32-bit number is at the highest byte address.

The channel engines within PCIO are big endian. The Bus Adapter performs the transformation described in TABLE 4-1, taking into account whether the data object is a data stream, programmed I/O or descriptor.

PCIO supports byte stacking when accessing the PROM and other devices on the EBus2. The 32-bit word assembled from successive reads of the 8-bit PROM/EBus2 is returned in little endian format. This is still compatible with CPU code fetches, which are always big endian, since the CPU bridge (U2P) incorporates a fixed byte lane alignment, converting the data in this case back to big endian.

# 4.4.2 Commands

PCI Local Bus reference: §3.1.1 and §3.1.2

PCIO responds to a limited number of PCI Bus commands, as summarized in TABLE 4-2. Note that in determining the number of cache lines to transfer, the 'Cache Line Size' value in the Configuration Space is utilized.

TABLE 4-2 PCI Bus Commands Implemented and Generated by PCIO

| C/BE<br>[3:0]# | Command Type                   | PCIO as Target                                                      | PCIO as Initiator                                                                         |

|----------------|--------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 101<br>0       | Configuration Read             | Implement                                                           | n/a                                                                                       |

| 101<br>1       | Configuration Write            | Implement                                                           | n/a                                                                                       |

| 011<br>0       | Memory Read                    | Treated identically, generates successive                           | Less than one full cache line                                                             |

| 111<br>0       | Memory Read Line               | transactions in the<br>CEI                                          | Exactly one cache line                                                                    |

| 110<br>0       | Memory Read<br>Multiple        |                                                                     | More than one cache line, or when the prefetch mechanism in bridge needs to be activated. |

| 011            | Memory Write                   | Treated identically,<br>generates successive<br>transactions in the | Less than one cache line, or a<br>non-integer number of cache<br>lines                    |

| 111<br>1       | Memory Write and<br>Invalidate | CEI                                                                 | One or more full cache lines                                                              |

Specifically, PCIO does not initiate Configuration commands, or initiate or implement Interrupt Acknowledge, Special Cycles, I/O Read or Write or Dual Address Cycle.

# 4.4.3 Basic Transfer Control

PCI Local Bus reference: §3.2.1

As an initiator, PCIO will not use IRDY# to force wait states into the transaction (i.e. PCIO is always ready to either source or receive data). As a target, PCIO will monitor IRDY# to properly control flow.

# 4.4.4 Addressing

PCI Local Bus reference: §3.2.2

As a target, PCIO does not implement the I/O address space; memory space accesses are performed only if linear burst ordering is requested, *i.e.* AD[1:0]=00. For any other encoding of AD[1:0], the transaction is disconnected after the first data phase.

As an initiator, only transactions with linear burst ordering are generated.

# 4.4.5 Byte Alignment

PCI Local Bus reference: §3.2.2 and 3.2.3

As a target, PCIO recognizes only a limited number of byte enable combinations, as summarized in Table 4-3. All other transactions will be terminated with targetaborts, except for configuration cycles, where any byte enable combination is allowed.

Table 4-3

| Transaction Type          | C/BE3# | C/BE2# | C/BE1# | C/BE0# |

|---------------------------|--------|--------|--------|--------|

| No-op (ignore)            | 1      | 1      | 1      | 1      |

| Byte at address 0x00      | 1      | 1      | 1      | 0      |

| Byte at address 0x01      | 1      | 1      | 0      | 1      |

| Byte at address 0x02      | 1      | 0      | 1      | 1      |

| Byte at address 0x03      | 0      | 1      | 1      | 1      |

| Half word at address 0x00 | 1      | 1      | 0      | 0      |

| Half word at address 0x02 | 0      | 0      | 1      | 1      |

| Word at address 0x00      | 0      | 0      | 0      | 0      |

| Error                     |        | Any O  | ther   |        |

Since successive data phases as a target are treated as individual transactions, byte enables can change between data phases.

As an initiator, PCIO will generate only byte, half-word and word transactions with encoding as in Table 4-3. Byte enables will not change between data phases.

# 4.4.6 Transaction Termination

PCI Local Bus reference: § 3.3.3

As a target, PCIO will never terminate a transaction with a retry, disconnect or target-abort, except as noted in Section 4.4.4 (non-linear burst ordering) and Section 4.4.5 (byte alignment).

As an initiator, PCIO will generate master-initiated terminations based on expiration of the latency timer and the status of the GNT# signal. Memory Write and Invalidate commands will ignore the latency timer until a cache line boundary is reached. Note that the channel engine is not notified of this condition, and the data transfer is restarted at the next memory address.

PCIO will generate master-abort terminations when no target responds to a command initiated by PCIO. The master-abort detected bit in the corresponding function's configuration space is set, and an error is reported to the channel engine, which will then generate an interrupt.

PCIO can deal with target retry and disconnect terminations, hiding this conditions from the channel engines requesting the transactions. Target-abort terminates the transactions and the channel engine gets notified of the error. There are no timeout counters or retry counters to recover from targets that do not respond properly.

# 4.4.7 Fast Back-to-Back

PCI Local Bus reference: §3.4.2

PCIO has the Fast Back-to-Back Capable bit hardwired to '1' in the Status register, indicating that, as a target, it meets the requirements for performing fast back-to-back cycles.

# 4.4.8 Arbitration Parking

PCI Local Bus reference: §3.4.3

PCIO does not require or expects the PCI Bus to be parked so that it is granted to it when no other agent is requesting it.

At the expense of an extra arbitration latency clock for other agents when the bus is IDLE, optionally parking PCIO will reduce its arbitration latency to zero clocks.

# 4.4.9 Latency

PCI Local Bus reference: §3.4.4

As a target, PCIO tries to minimize target latency whenever possible. Slave writes are buffered at the EBus2 channel engine, so that latency should be minimized. Register writes to internal PCIO locations have relatively fast throughput as well.

Slave reads from internal PCIO locations, although not buffered, are relatively fast, possibly in the order of four PCI clocks. However, if a slave read starts when a DMA write transaction is taking place in the CEI, the slave read will be held until the write finishes, since they both use the same CEI resource. For a 64-byte burst on with a 32bit word size, this can be up to 16 clocks.

**Note –** Version 2.1 of the PCI Specification recommends/requires slave reads expected to take more than 16 clock cycles to be disconnected (pseudo split transaction). PCIO does not implement this feature. Moreover, in the case of bytestacked reads to slow EBus2 devices, read latencies can be very high.

Slave reads from the EBus2 devices, or slave writes when the write buffers are backed up, have their latency determined by the timing of the external devices, some of which are rather slow. In addition, the EBus2 can be busy with a DMA transfer resulting in additional latency. Yet another source of latency is byte stacking from the PROM.

As an initiator, PCIO contains internal buffering for each of its internal functions to minimize the impact of bus latency. PCIO will generate burst of up to 64 bytes directed, under normal circumstances, to the host bridge (U2P). Assuming a relatively short delay for the first target-ready, and one data phase per clock thereafter, Min\_Gnt should be set to about 24 clock cycles.

#### 4.4.10 **Exclusive Access**

PCI Local Bus reference: §3.5

PCIO does not implement or support exclusive access and does not have a LOCK# signal.

#### 4.4.11 Device Selection

PCI Local Bus reference: §3.6.1

PCIO will assert DEVSEL# when selected as a target at 'medium' speed (i.e. two clocks after assertion of FRAME#). This facilitates design of a synchronous interface, and does not affect performance, since internal transactions can proceed in parallel with assertion of DEVSEL#.

# **Channel Engine Interface**

The Channel Engine Interface is a modular, bus-independent interconnect intended to serve as the backbone of the FEPS and PCIO designs.

# 5.1 Goals

The Channel Engine Interface (CEI) has the following goals:

- Modular

- Extensible (number of master and slave ports)

- Bus-independent and free of external timing constraints, but closely resemble SBus protocol

- Interface speed limited by existing ASIC technology

# 5.2 Terminology/Glossary

*Channel Engine Interface (CEI)* refers to the interconnect mechanism and protocol between the Channel Engines and Bus Adapter.

Bus Adapter refers to all the logic between the CEI and the external bus.

*Channel Engine* refers to each of the individual, self-contained functional blocks in PCIO: Ethernet and EBus2.

*Port* refers to the connection of a Channel Engine to the CEI. A Channel Engine can have master or slave ports, or both.

Double Word refers to a 64-bit word (8 bytes), moved in a single data beat on the CEI.

# 5.3 Signals

Signals in the CEI are either shared, going from the Bus Adapter to all of the Channel Engines, or dedicated, going from one Channel Engine to the Bus Adapter or vice versa.

The signals are summarized in Table 5-1. "Direction" is indicated as seen from the Channel Engine perspective (*i.e.* "input" means driven by Bus Adapter and received by Channel Engine). All signals are active high, with the exception of ce\_sack[2:0]\_l and ce\_drack[2:0]\_l, which follow the SBus encoding.

Table 5-1 Channel Engine Interface Signals

| Signal Name    | Direction         | Function                                                                                                                                                                                                                                                                            |  |

|----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General        | •                 |                                                                                                                                                                                                                                                                                     |  |

| ce_rst         | Input, shared     | Reset, either hardware/power-on of from test control logic                                                                                                                                                                                                                          |  |

| ce_clk         | Input, shared     | Channel Engine interface clock. All signals are synchronous to this clock. Maximum frequency is determined by ASIC technology and is at least 33 MHz + 10%                                                                                                                          |  |

| Datapath       |                   |                                                                                                                                                                                                                                                                                     |  |

| ce_dout[63:0]  | Output, dedicated | Multiplexes master address (32-bit) and transaction size/type, master data (32/64-bit) and slave data (32-bit)                                                                                                                                                                      |  |

| ce_din[63:0]   | Input, shared     | Multiplexes master data (32/64-bit), slave address and size and slave data (32-bit)                                                                                                                                                                                                 |  |

| Slave Port     |                   |                                                                                                                                                                                                                                                                                     |  |

| ce_sel         | Input, dedicated  | Slave select, indicates the start of a slave transaction, remain asserted until the transaction is completed                                                                                                                                                                        |  |

| ce_sack[2:0]_1 | Output, dedicated | Slave acknowledge, issued by the slave to indicate acceptance of data or data ready. The encoding is as follows:  111 — Idle/Wait  110 — Error acknowledge  101 — Byte acknowledge  011 — Word (32-bit) acknowledge  001 — Half-word (16-bit) acknowledge  100, 010, 000 — Reserved |  |

Table 5-1

Channel Engine Interface Signals (Continued)

| Master Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Signal Nama         | Direction         | Function                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ce_br                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                   | Direction         | runction                                                                                                                                                                                                                                                              |

| Input, dedicated   Bus grant, issued by the Bus Adapter to a specific master port when it is ready to perform a DMA transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Master Port         | Г                 |                                                                                                                                                                                                                                                                       |

| specific master port when it is ready to perform a DMA transaction  ce_drack[2:0]_1  Input, shared  DMA read acknowledge, issued by Bus Adapter to indicate data is ready during DMA reads. Data follows ce_drack_l on the next clock cycle. Encoding is as follows:  111 — Idle/Wait 110 — Error acknowledge 101 — Byte acknowledge 101 — Half-word (16-bit) acknowledge 100, 010, 000 — Reserved  ce_dwack  Input, shared  DMA write acknowledge, issued by Bus Adapter to indicate it can accept new data from Channel Engine. Bus Adaptor latches data on the same clock edge it issues the acknowledge.  ce_memdone  Input, dedicated  DMA write transaction done, is issued by the Bus Adapter when a previously posted CEI transaction actually completes on the external bus  Error and Exception  Reporting  ce_lerr  Input, shared  Late Error, is issued by Bus Adapter (in SBus systems) if sb_lerr_ is detected after a DMA read operation. Masters must monitor ce_lerr exactly two clock cycles after each n0n-idle ce_drack_l  ce_drack_l  DMA Write Error, is issued by the Bus Adapter together with ce_memdone to indicate sb_lerr_was detected or a bus error occurred during a DMA write transaction.  Parity Error, is issued by the bus adapter during slave port write access or a DMA read transaction, to indicate a parity error on the external bus. | ce_br               | Output, dedicated | needs to perform a read or write DMA                                                                                                                                                                                                                                  |

| Adapter to indicate data is ready during DMA reads. Data follows ce_drack_l on the next clock cycle. Encoding is as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ce_bg               | Input, dedicated  | specific master port when it is ready to perform                                                                                                                                                                                                                      |

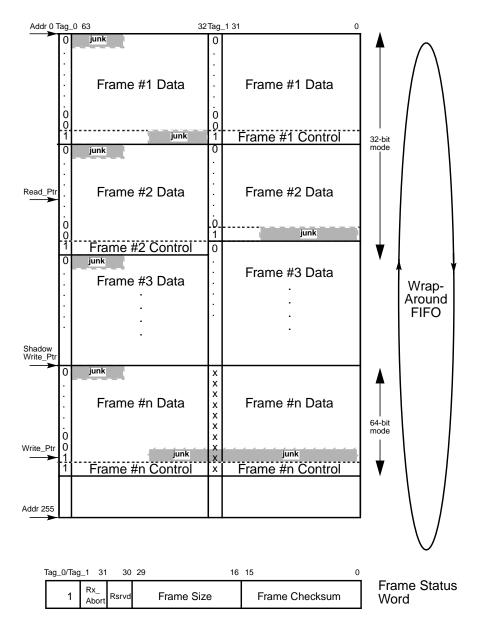

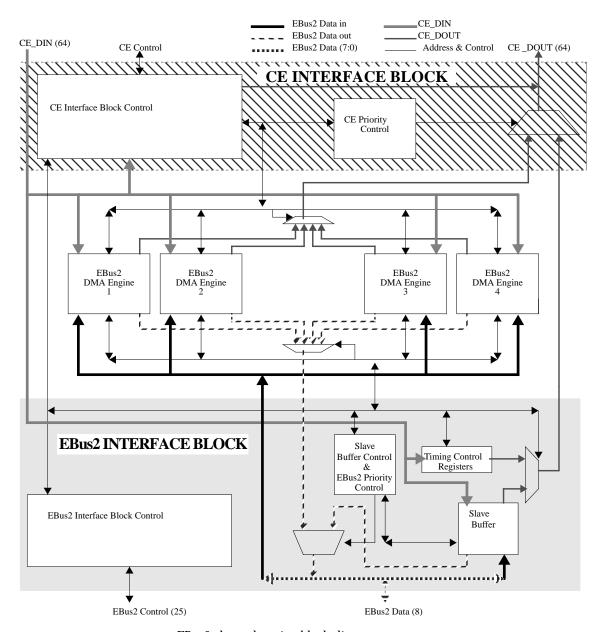

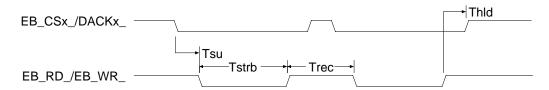

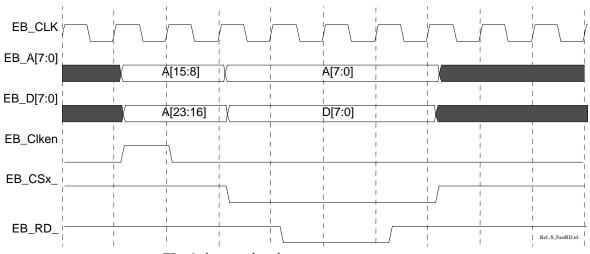

| Adapter to indicate it can accept new data from Channel Engine. Bus Adaptor latches data on the same clock edge it issues the acknowledge.  Ce_memdone Input, dedicated DMA write transaction done, is issued by the Bus Adapter when a previously posted CEI transaction actually completes on the external bus  Error and Exception Reporting  Ce_lerr Input, shared Late Error, is issued by Bus Adapter (in SBus systems) if sb_lerr_ is detected after a DMA read operation. Masters must monitor ce_lerr exactly two clock cycles after each n0n-idle ce_drack_l  Ce_dwerr Input, shared DMA Write Error, is issued by the Bus Adapter together with ce_memdone to indicate sb_lerr_ was detected or a bus error occurred during a DMA write transaction  Ce_perror Input, shared Parity Error, is issued by the bus adapter during slave port write access or a DMA read transaction, to indicate a parity error on the external bus.                                                                                                                                                                                                                                                                                                                                                                                                                                     | ce_drack[2:0]_l     | Input, shared     | Adapter to indicate data is ready during DMA reads. Data follows ce_drack_l on the next clock cycle. Encoding is as follows:  111 — Idle/Wait  110 — Error acknowledge  101 — Byte acknowledge  011 — Word (32-bit) acknowledge  001 — Half-word (16-bit) acknowledge |